# Dominant growth directions in integrated ciruit technology: 3D device architectures, 3D heterogeneous integration and Silicon Carbide

Andrzej J. Strójwąs

**PDF Solutions Inc. and Carnegie Mellon University**

**ELTE 2023, Ryn, 19 kwietnia 2023**

#### **Outline**

- Current technology landscape and future growth directions

- 3D device structures from FinFET to nanosheet architectures and beyond Silicon

- 3D heterogeneous integration: chiplets and neuromorphic computing

- Electrical car driven SiC market explosion

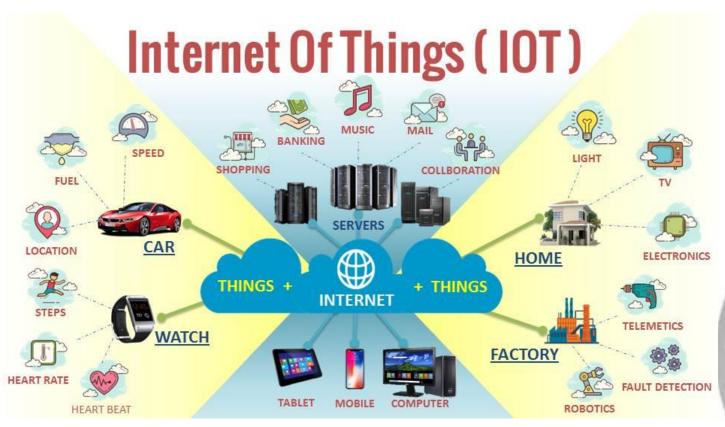

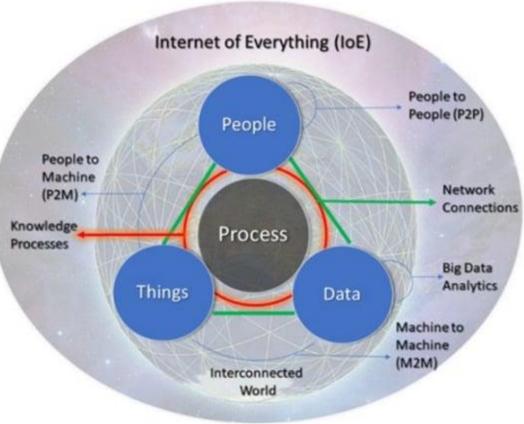

# From Inetrnet of Things to Internet of Everything

#### **Infrastructure Requirements**

- Data Availability/Connectivity (5G/6G)

- > Artificial Intelligence Algorithms

- Computing Power and Massive Data Storage

- Data Analytics

- > Intelligent System Implementation (cars, cities,...)

#### **Artificial Intelligence Methods**

- Machine Learning Without Human Intervention

- Deep Learning Deployment of neural networks on huge data sets

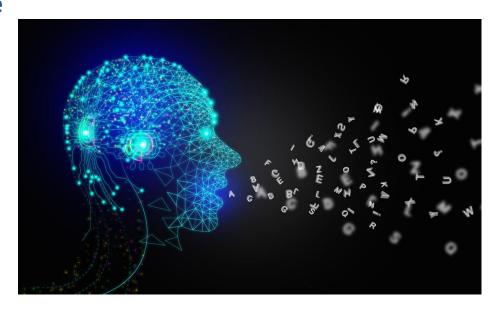

- ➤ Generative AI Creation of new data, text, audio, video. Text is generated in natural language using Large Language Models (LLM)

- ➤ ChatGPT Most popular system nowadays. Can answer any questions, pass any exam, write a poem, compose a song, create an impressive painting, etc.

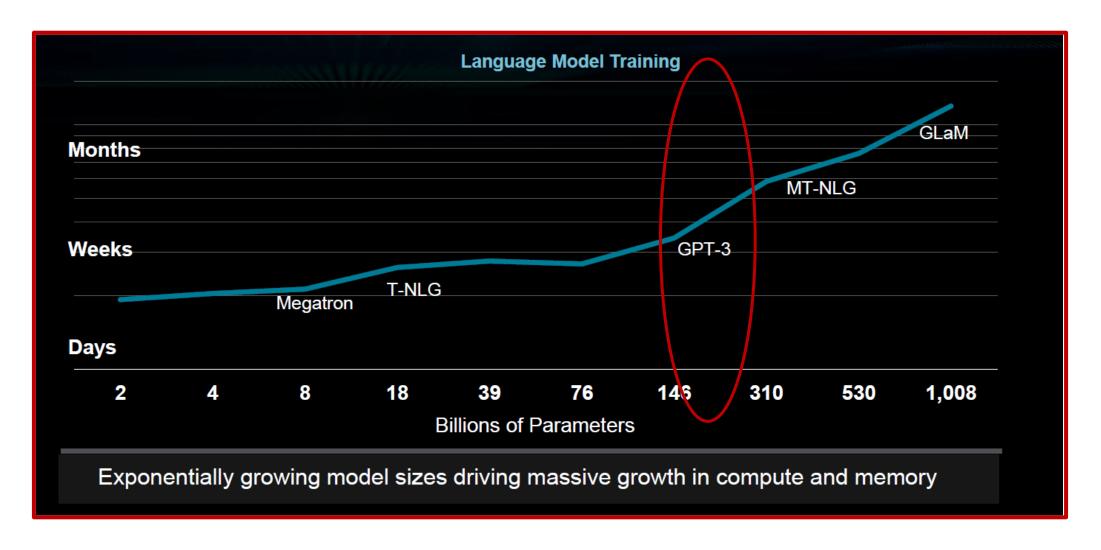

**But...** What are the computing and storage needs to train such a system?

# **Training Needs of the Large Language Models**

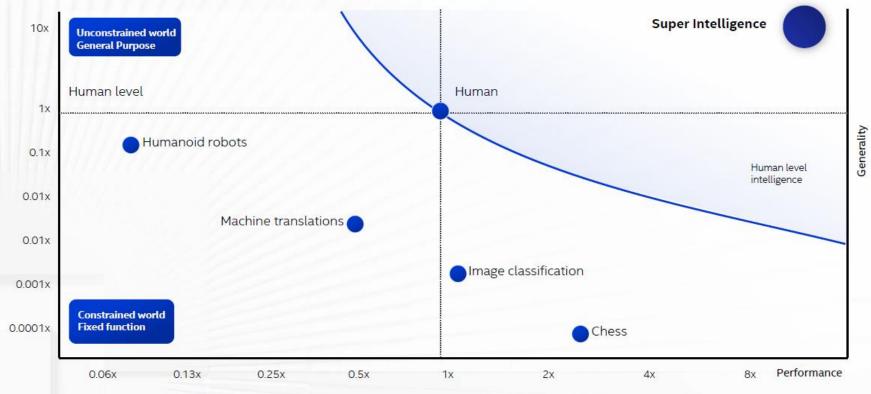

# **Artificial Intelligence Evolution**

How do we approach human brain capabilities?

- > So far successes only for the application specific systems (robotics, image classification, chess,...

- Achieved with huge compute and storage resources with huge energy consumption

- > Human brain: almost 100 billion neurons, up to 1,000 trillion synapses, but...

- Power consumption below 20 W

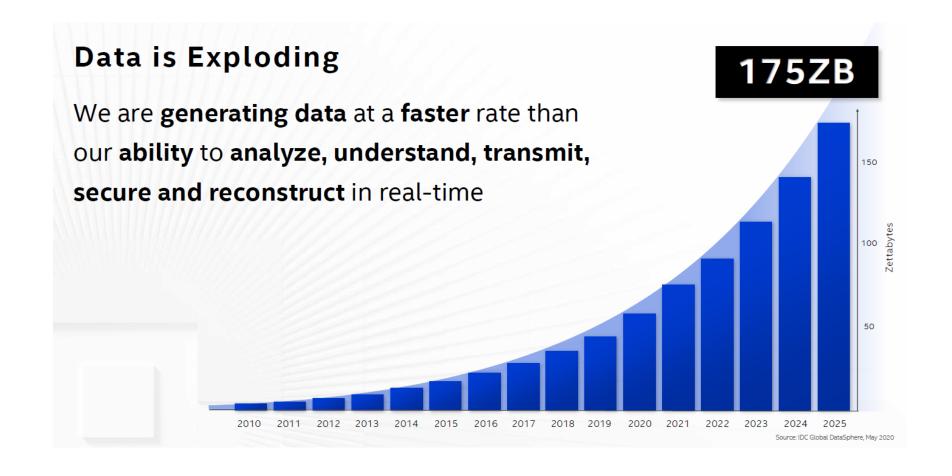

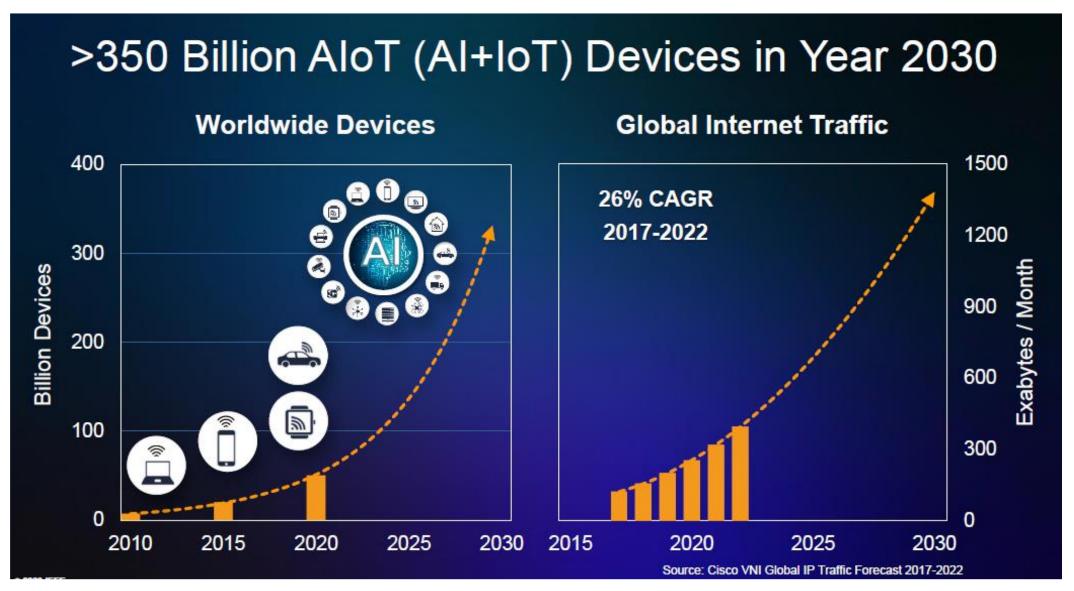

#### **Evolution of Market Drivers: Data Explosion**

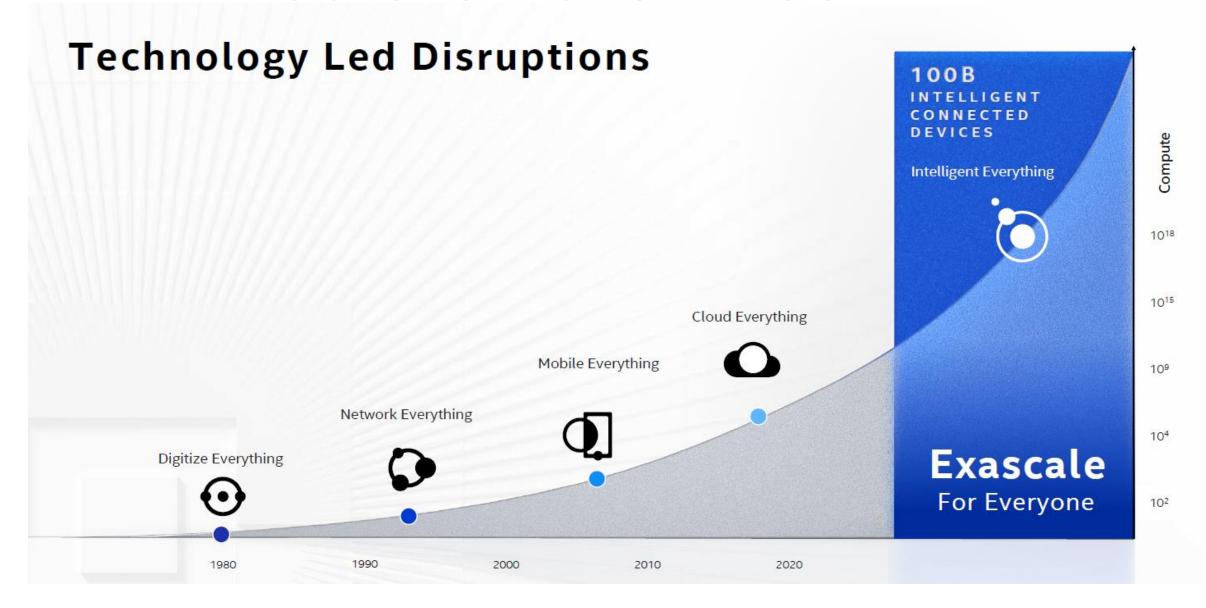

#### **Evolution of Market Drivers**

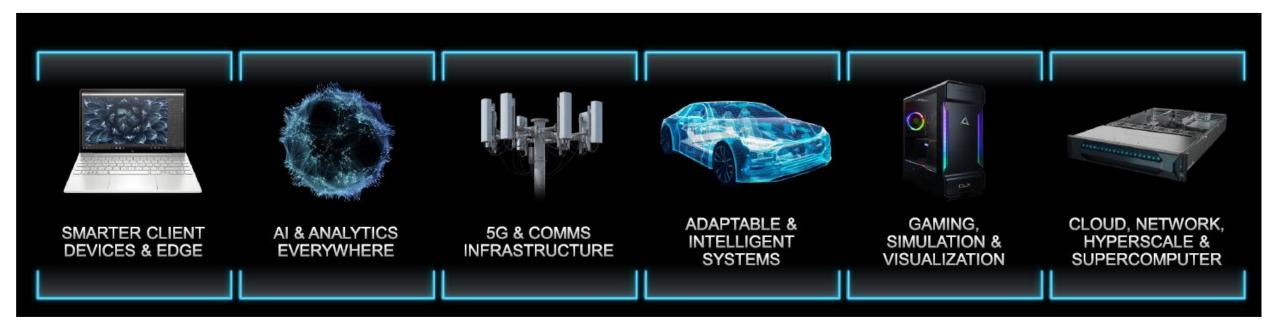

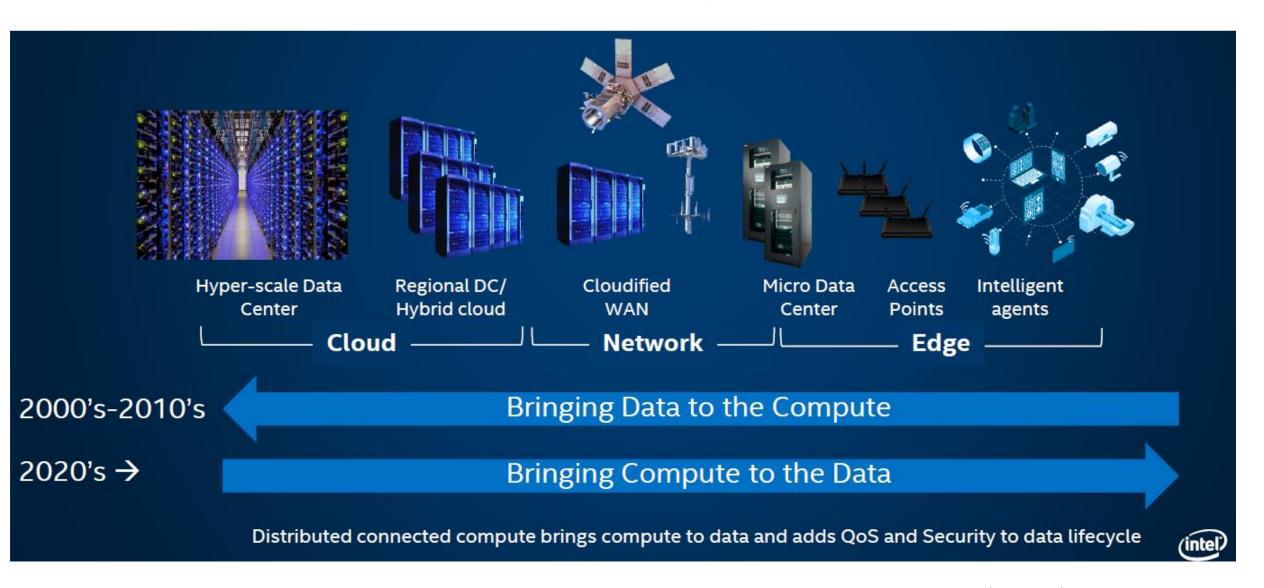

#### **Distributed Compute Era**

#### **Edge AI Device Trajectory**

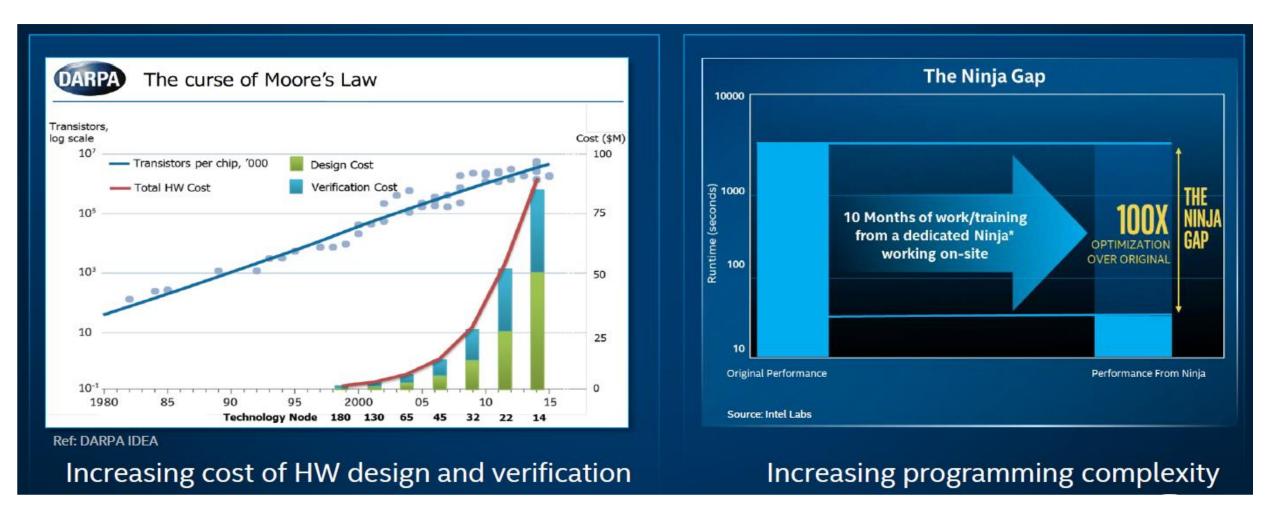

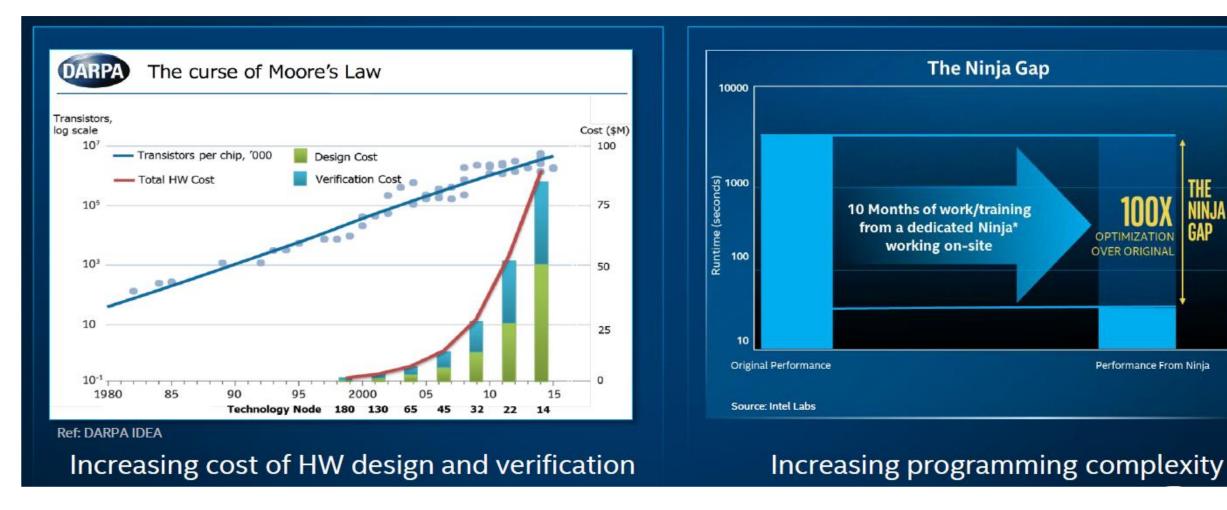

#### **Compute Barriers: Complexity and Cost**

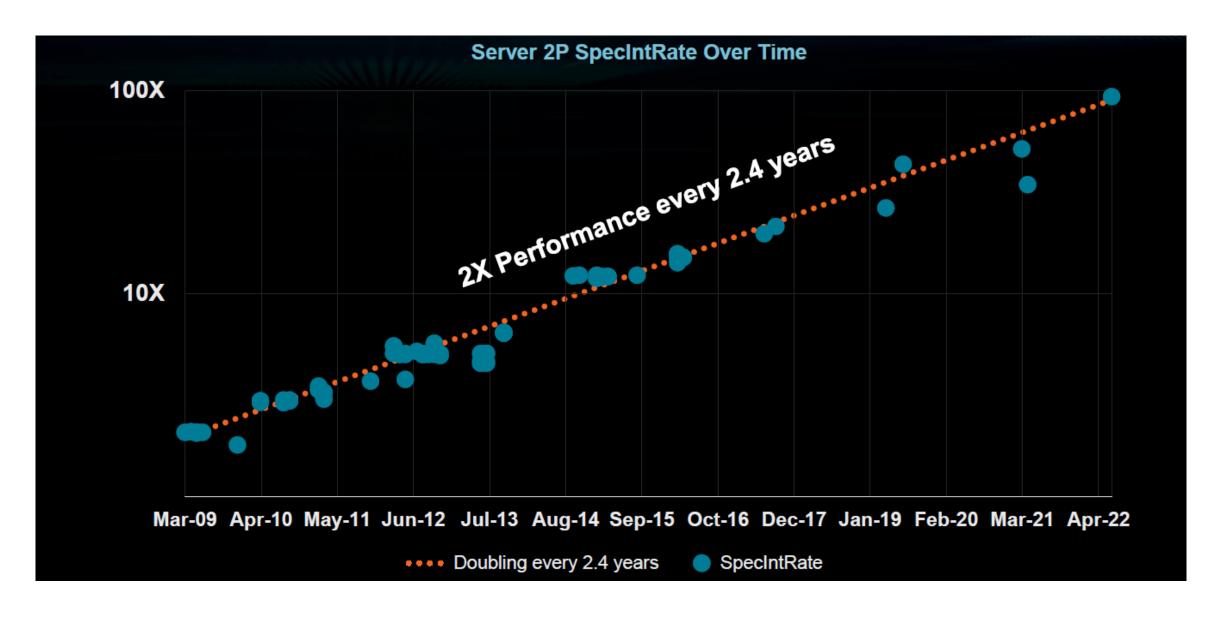

#### **Data Server Performance Evolution**

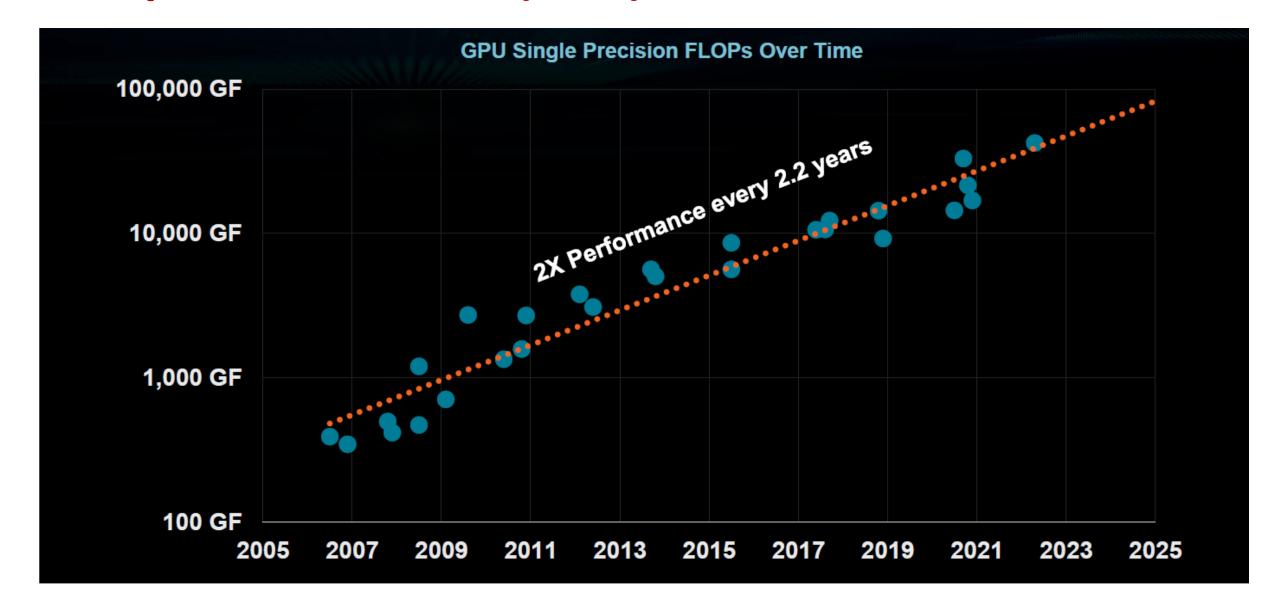

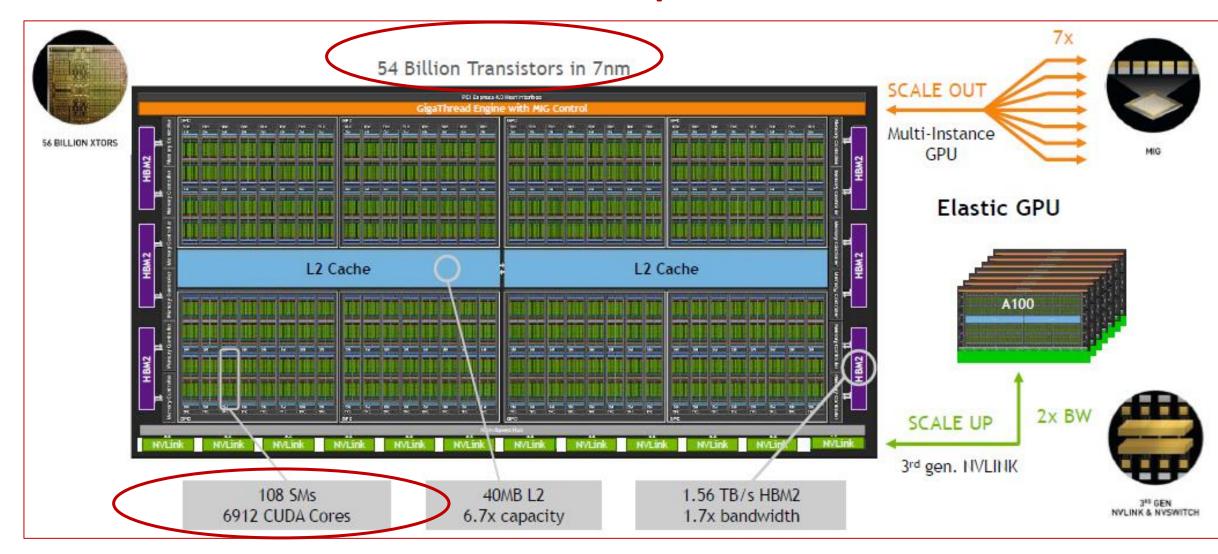

# **Graphical Processor (GPU) Performance Evolution**

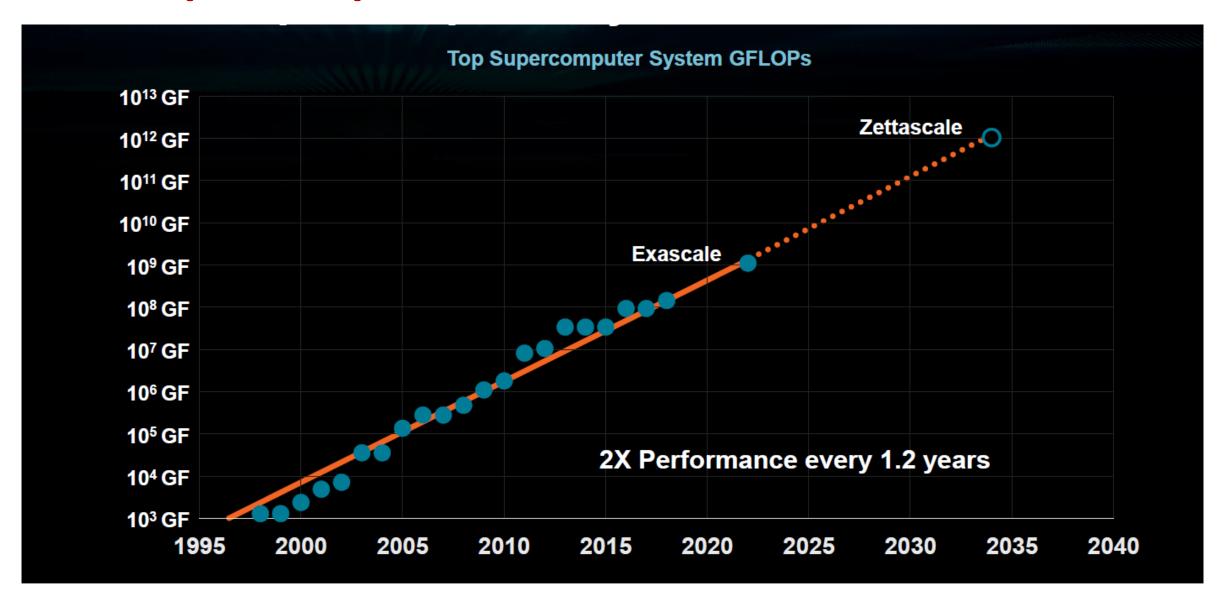

#### **Supercomputer Performance Evolution**

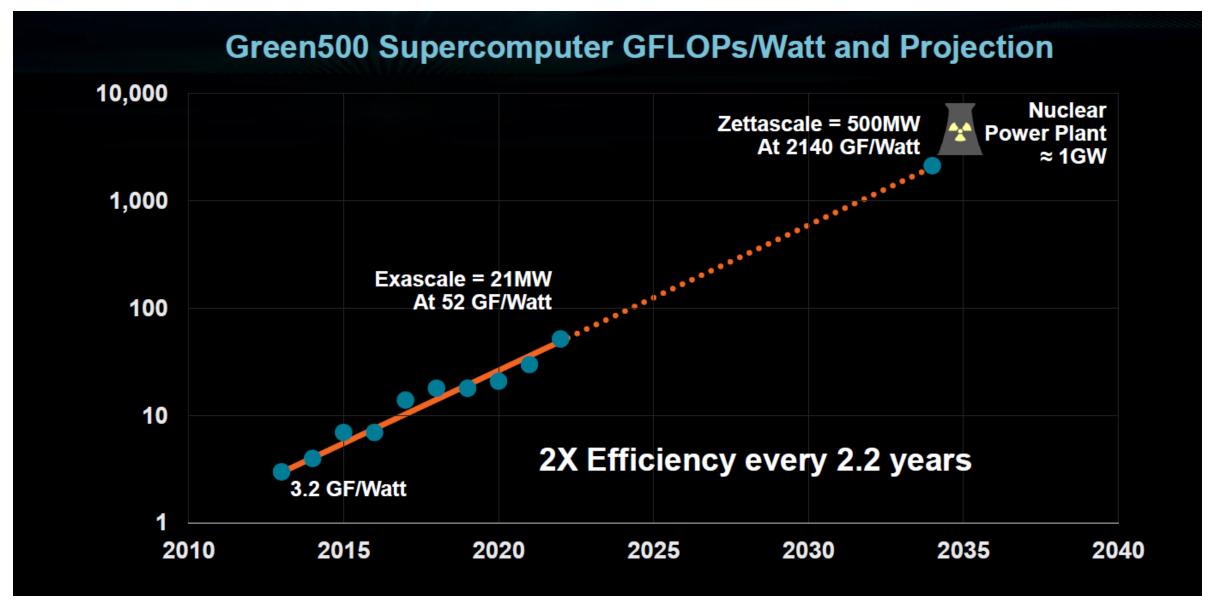

# Performance/Power Consumption Evolution

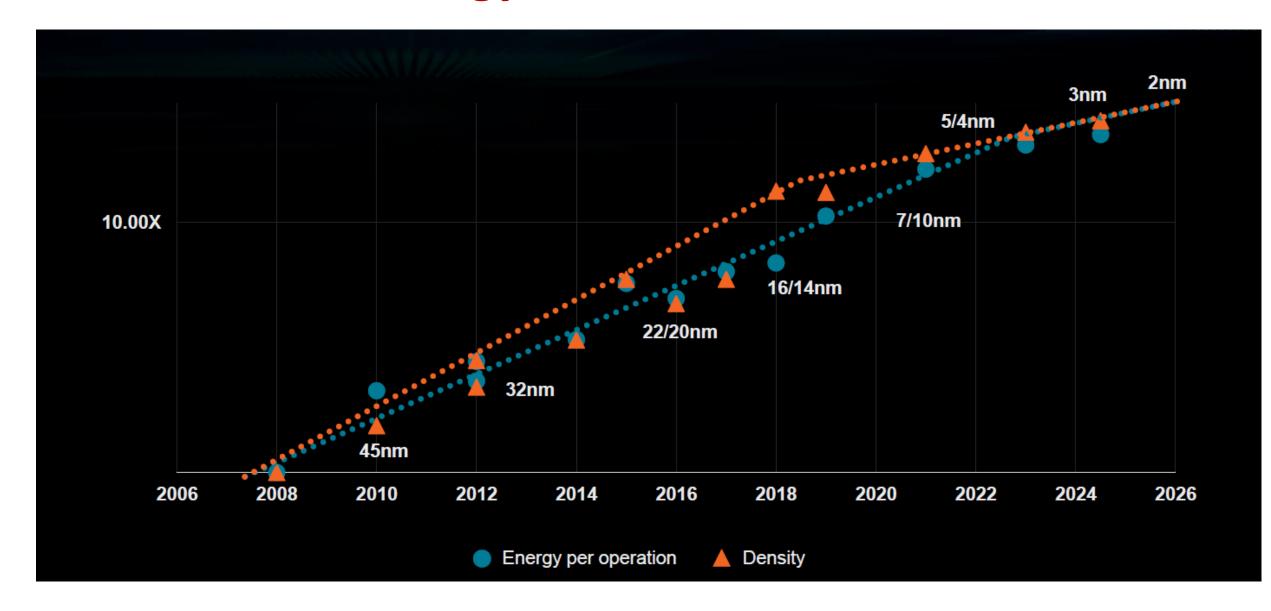

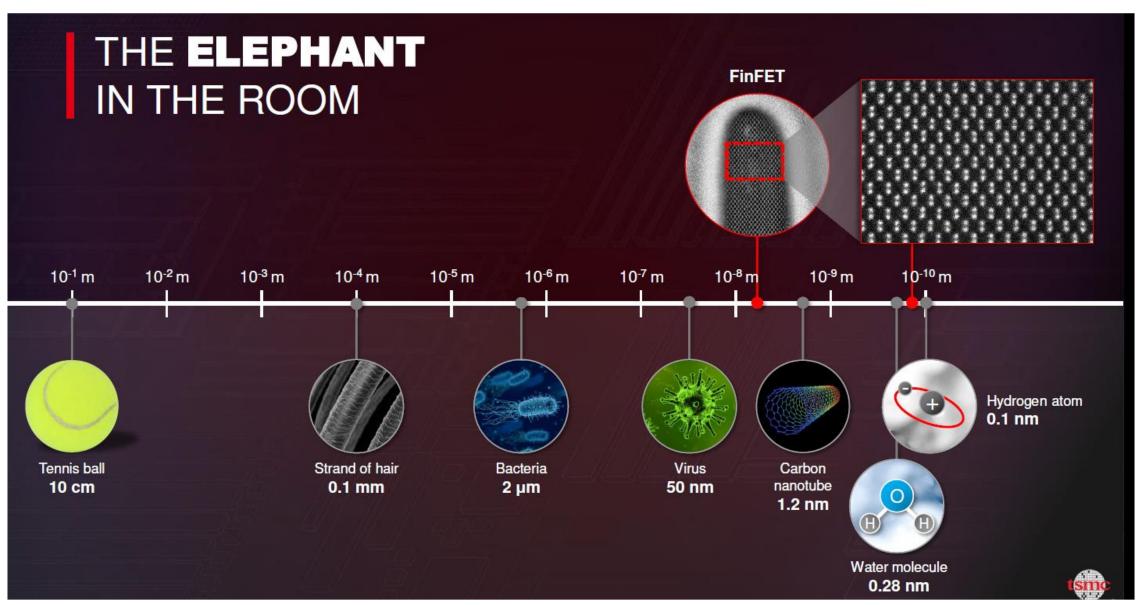

# **ULSI Technology Miniaturization**

#### **Miniaturization Scale**

#### **Key Barriers: Complexity and Costs**

# **Solution: Massively Parallel Architecture**

**NVIDIA: A100 Chip**

# **Solution: Wafer Scale Integration?**

# Cerebras Wafer-Scale Engine (WSE-2)

The Largest Chip in the World

850,000 cores optimized for sparse linear algebra

46,225 mm<sup>2</sup> silicon

2.6 trillion transistors

40 gigabytes of on-chip memory

20 PByte/s memory bandwidth

220 Pbit/s fabric bandwidth

**7nm** process technology

56x larger than largest GPU

#### **Outline**

- Current technology landscape and future growth directions

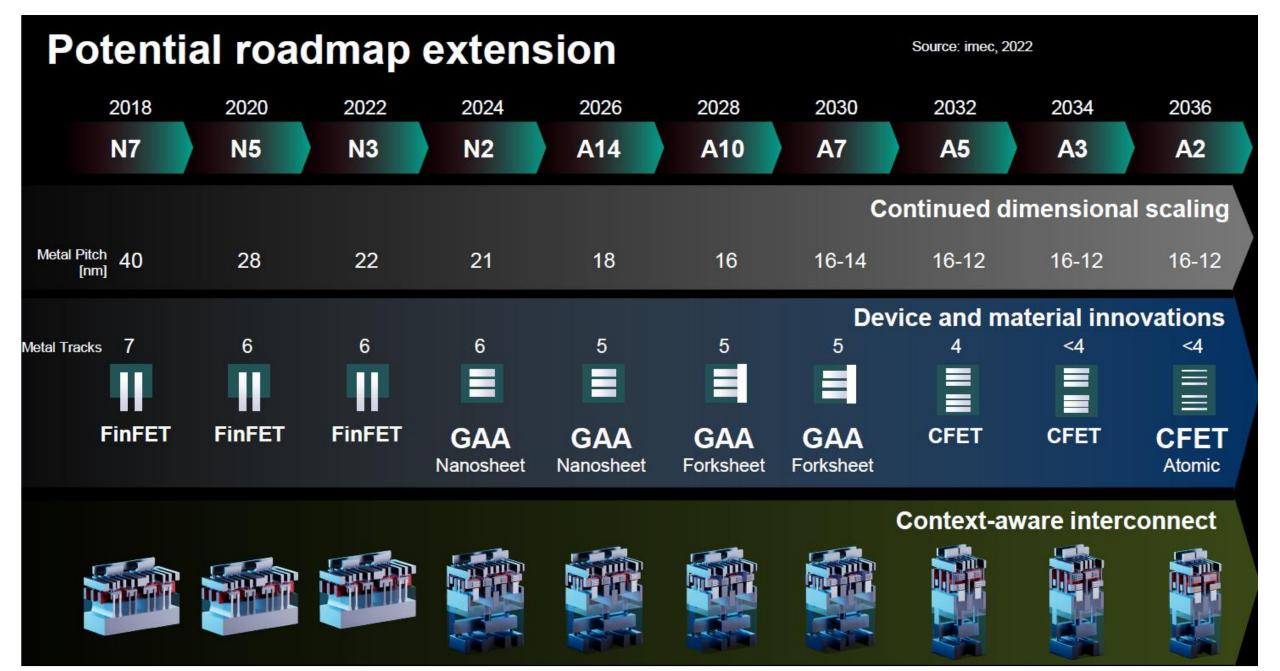

- 3D device structures from FinFET to nanosheet architectures and beyond Silicon

- 3D heterogeneous integration: chiplets and neuromorphic computing

- Electrical car driven SiC market explosion

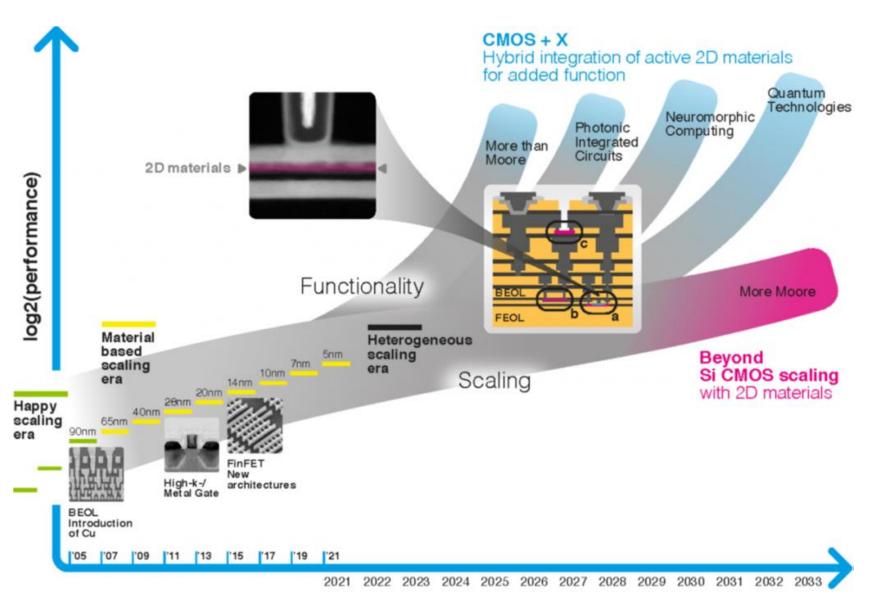

Source: imec, 2023

#### Disruptive architecture innovations

**Nanosheet**

Source: imec, 2023

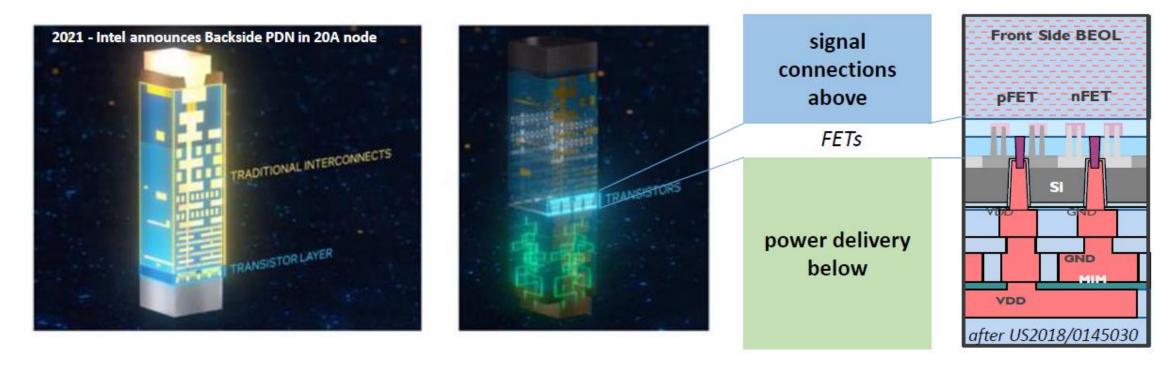

# Next step in differentiation: backside power delivery

- backside power delivery allows next-level differentiation of signal wiring and power delivery

- → big Integration challenge

Year of 1st introduction

#### **Outline**

- Current technology landscape and future growth directions

- 3D device structures from FinFET to nanosheet architectures and beyond Silicon

- > 3D heterogeneous integration: chiplets and neuromorphic computing

- Electrical car driven SiC market explosion

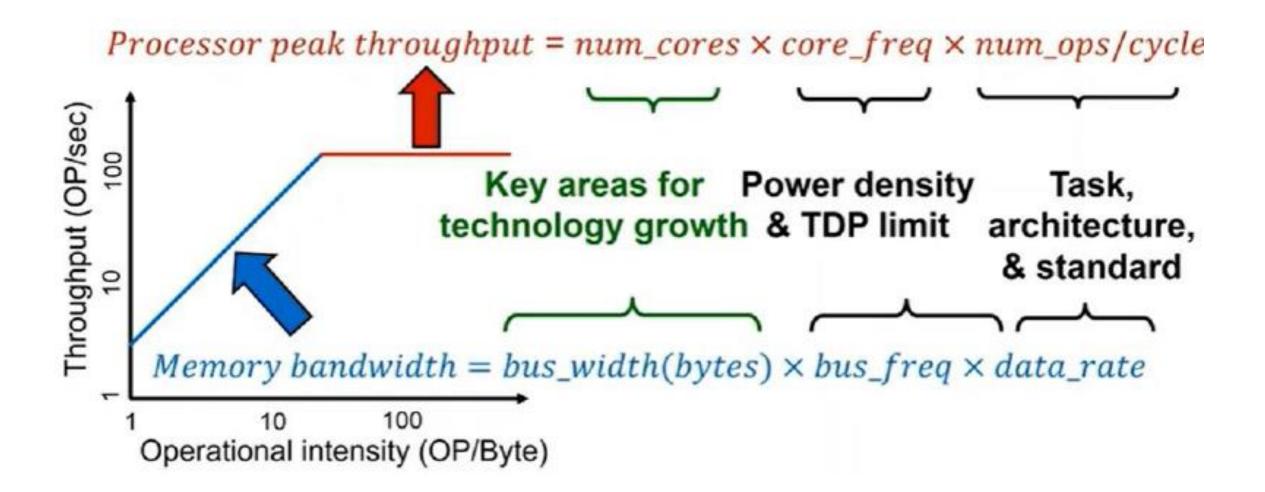

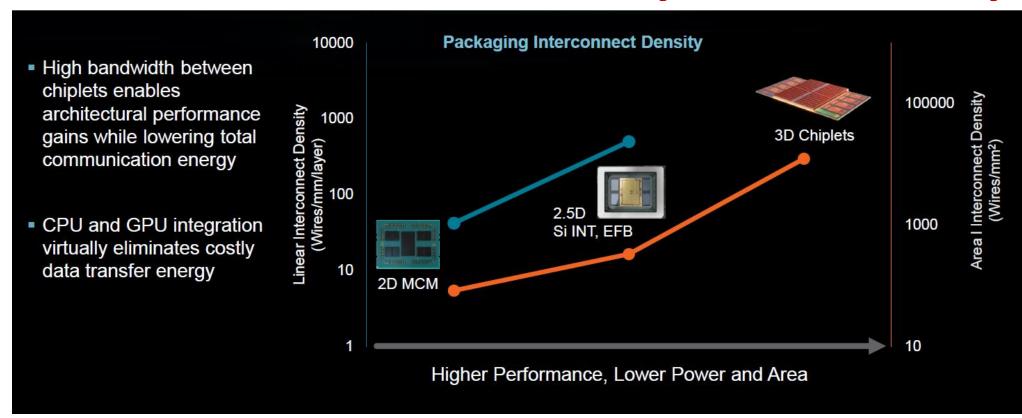

#### **System Performance Roofline Plot**

# How Do We further Increase System Efficiency?

- > 2.5 D & 3D Integration

- ➤ More than 90% of Power Consumption for Processor-Memory Communication

- ➤ Near Memory and In-Memory Computing next on roadmap

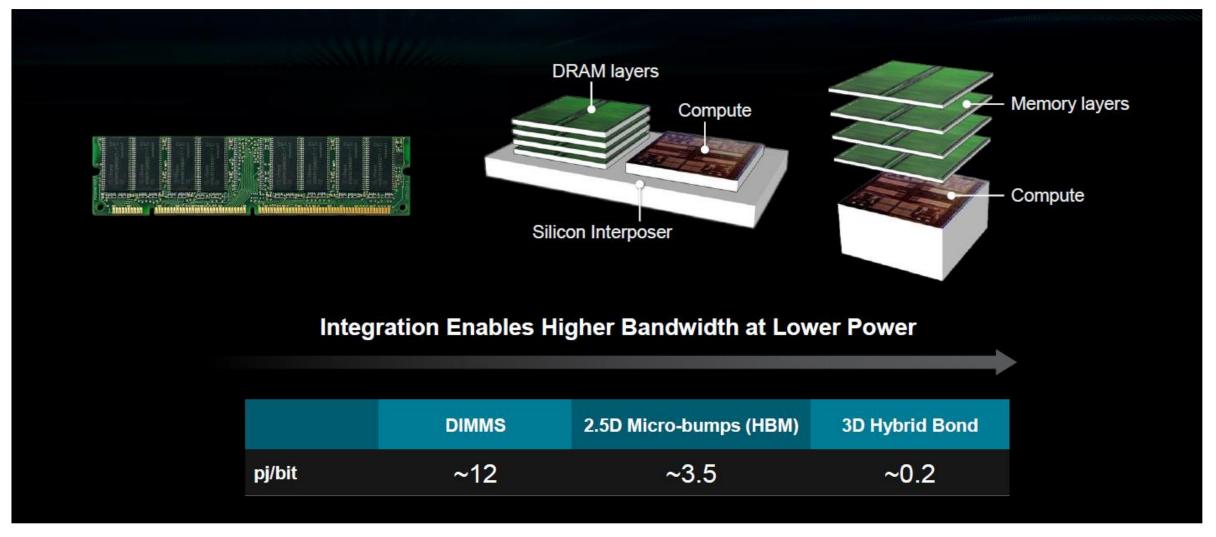

# **Energy Benefits of 2.5D & 3D Integration**

Amount of energy to send data from the processor to DRAM

> 2D - 12pJ/bit

2.5D - 3.5 pJ/bit

3D - .2pJ/bit

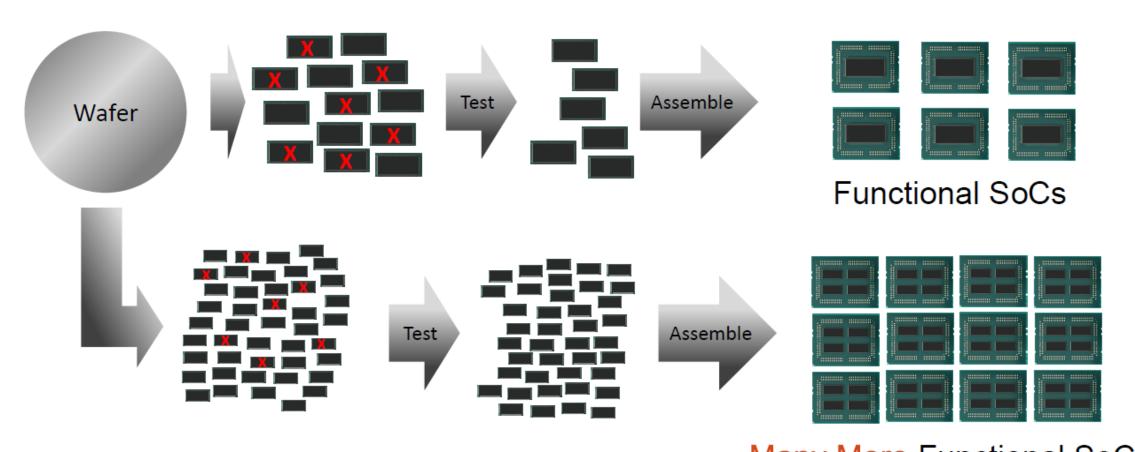

# **Additional Benefits to Chiplets: Higher Yield**

Many More Functional SoCs

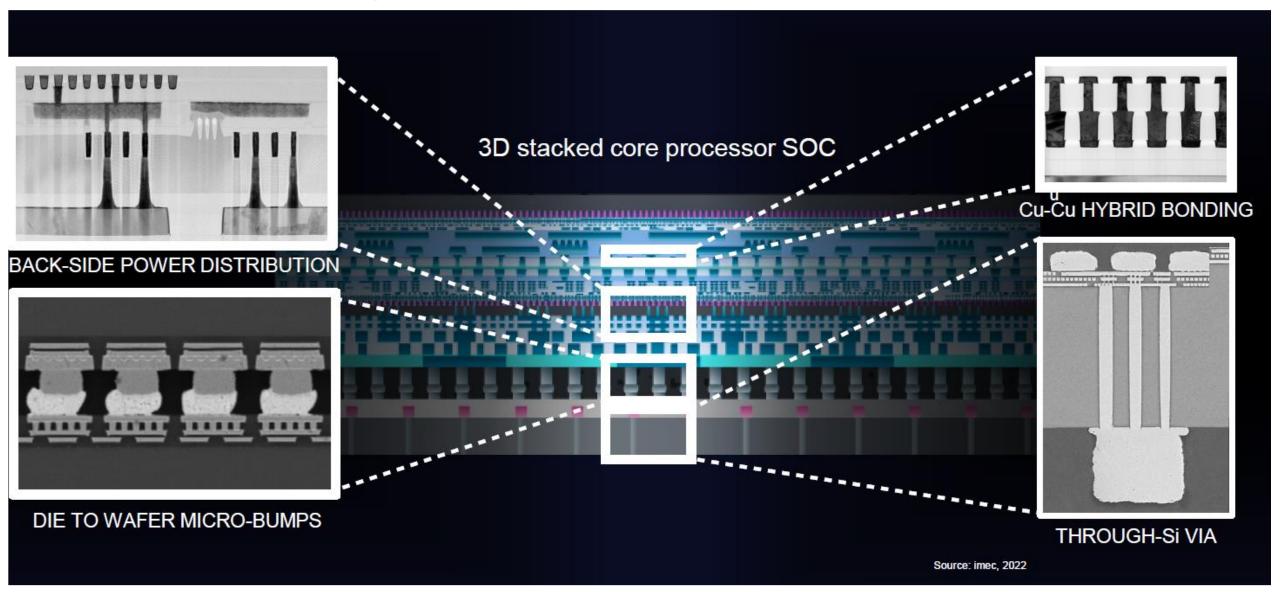

# **3D Integration Examples**

#### **3D Integration Roadmap**

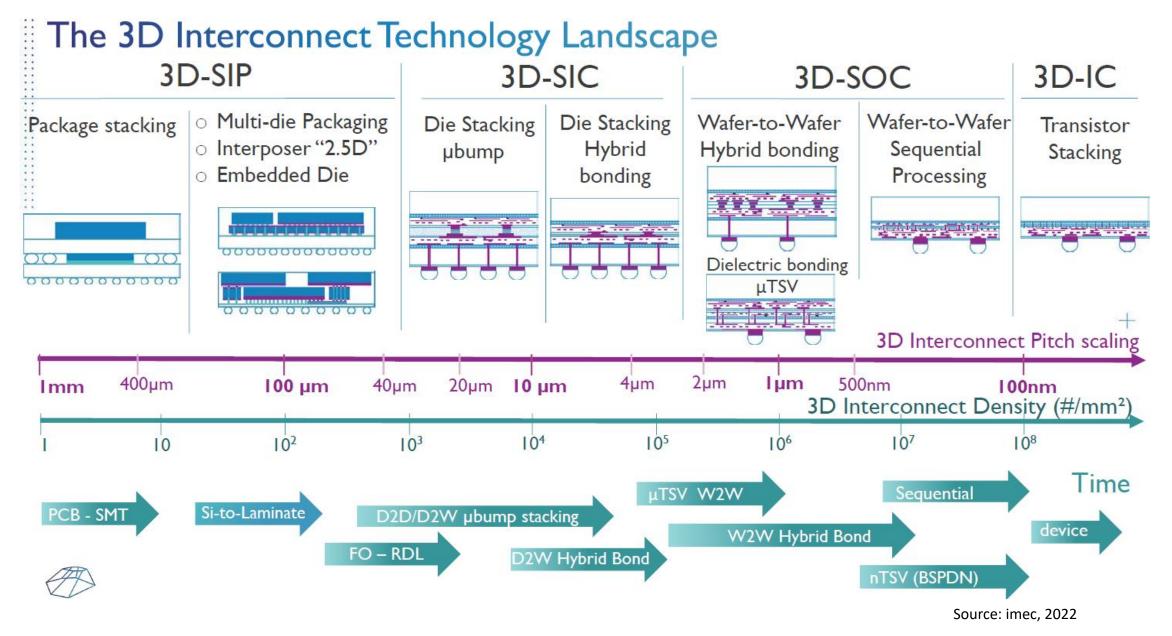

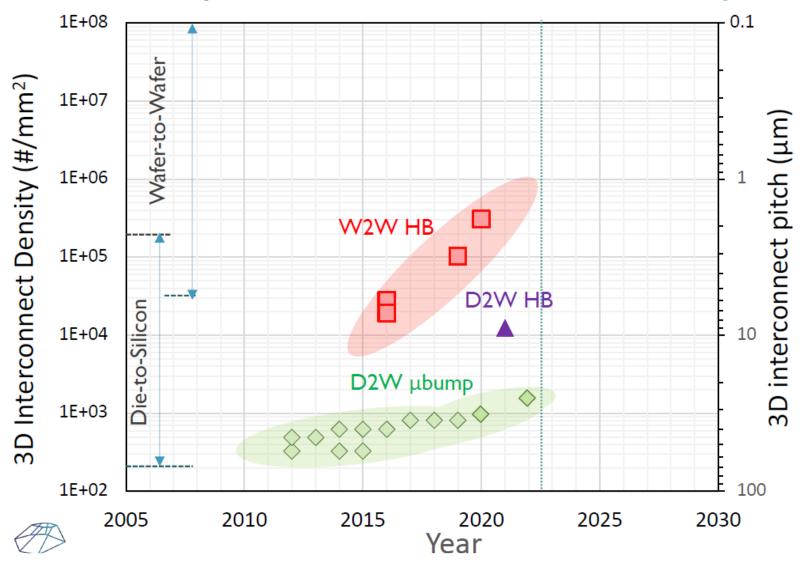

#### 3D Landscape and 3D Interconnect Roadmap

- Wafer-to-Wafer Hybrid bonding

- Die-to-Wafer

Hybrid bonding

- Die-to-WaferFlip-chip μBump

D2W= Die-to-wafer bonding W2W= Wafer-to-Wafer bonding HB= Hybrid bonding

Source: imec, 2022

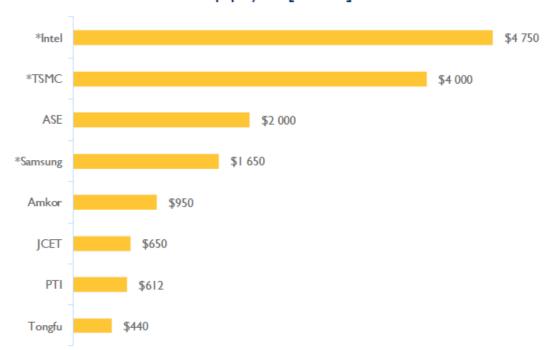

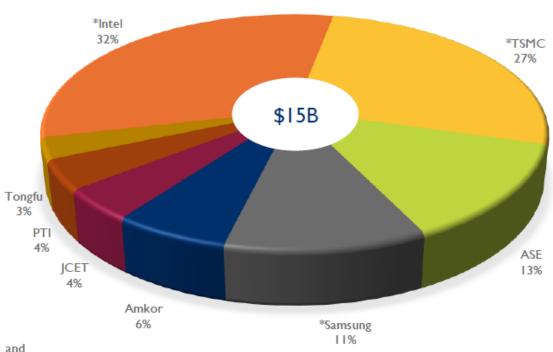

#### 2022 CAPEX HIGHLIGHTS FOR ADVANCED PACKAGING PLAYERS

#### Estimated 2022 CapEx spending for Packaging activity by top players [M US\$]

#### Estimated 2022 packaging CapEx split (top players)

\*Intel, TSMC and Samsung advanced packaging CapEx were estimated based on earnings calls statements and recent announcements of investments, since packaging is not their main business focus

All CapEx data is estimated based on information gathered during Q1 2022

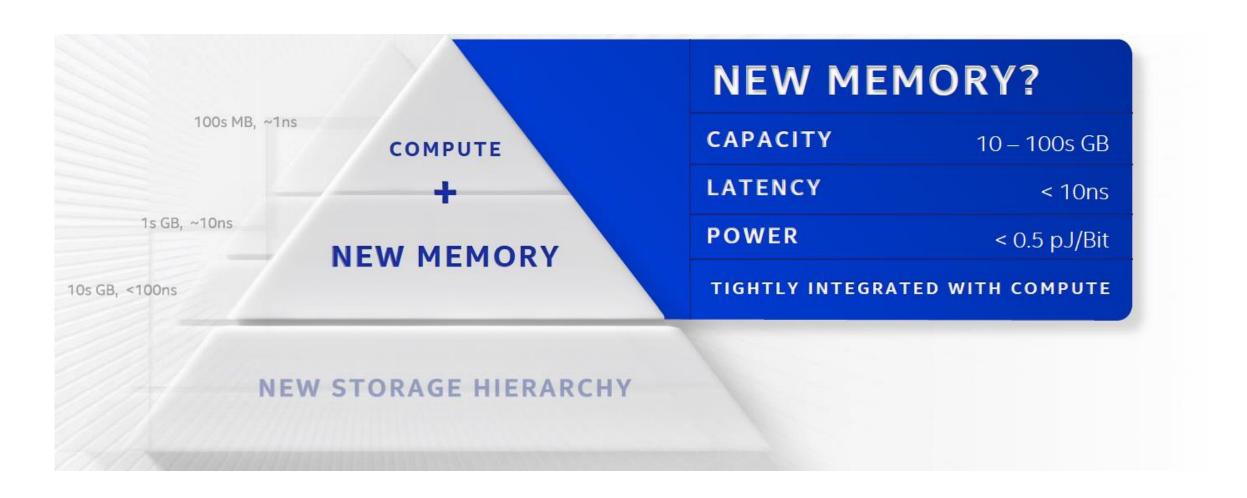

# Memory/Storage Hierarchy: New Memory Needs

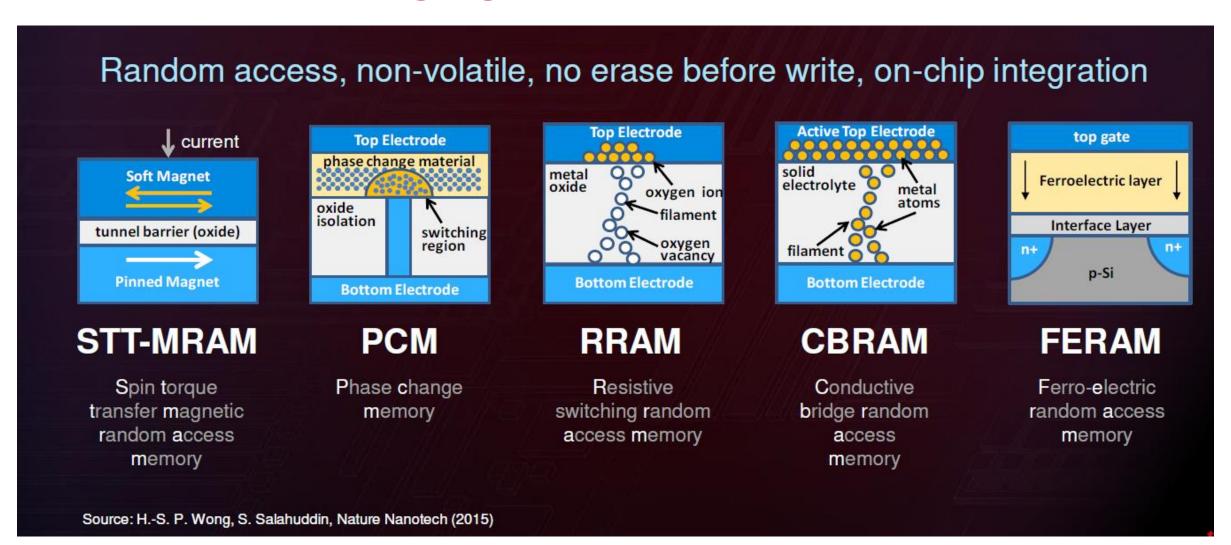

#### **Emerging Non-Volatile Memories**

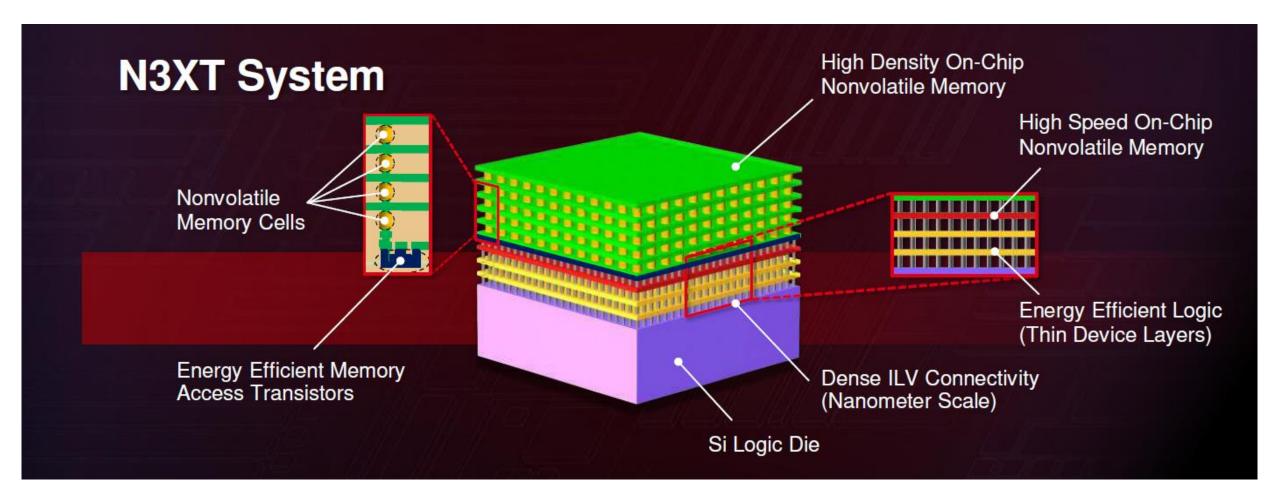

#### **Net Steps on Roadmap: Neuromorphic Computing**

Goal: Approach human brain neuron density with acceptable power consumption

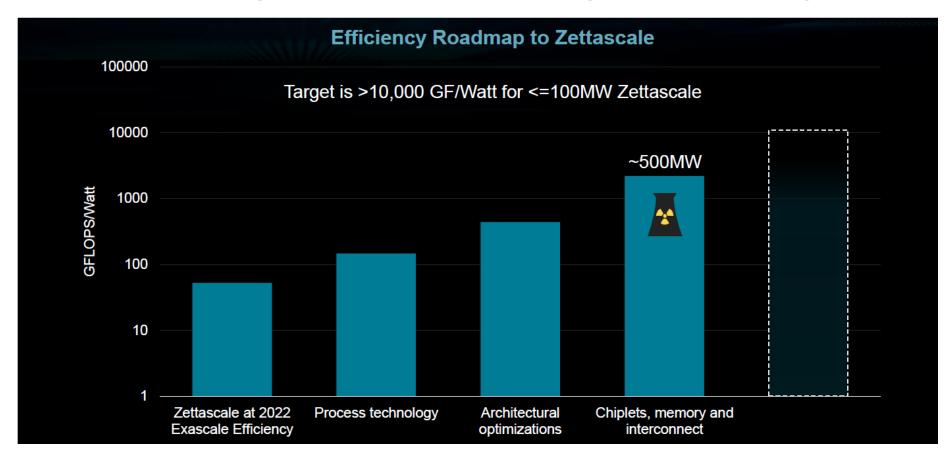

#### **Conclusions: System Efficiency Roadmap**

#### **Dominant Directions:**

- Further technological advances: device architectures, backside power delivery, emerging memories, 2D material, Carbon Nanotubes

- > System Architecture Optimization (software-hardware co-design, neuromorphic computing)

- 3D Heterogeneous Integration including Photonics

Source: L. Su AMD, ISSCC 2023

#### **Outline**

- Current technology landscape and future growth directions

- 3D device structures from FinFET to nanosheet architectures and beyond Silicon

- **❖** 3D heterogeneous integration: chiplets and neuromorphic computing

- Electrical car driven SiC market explosion

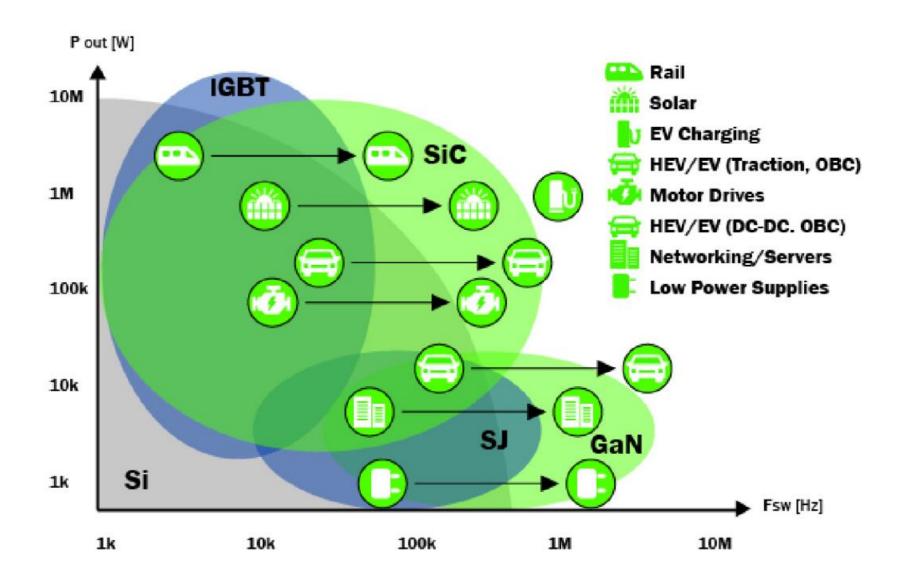

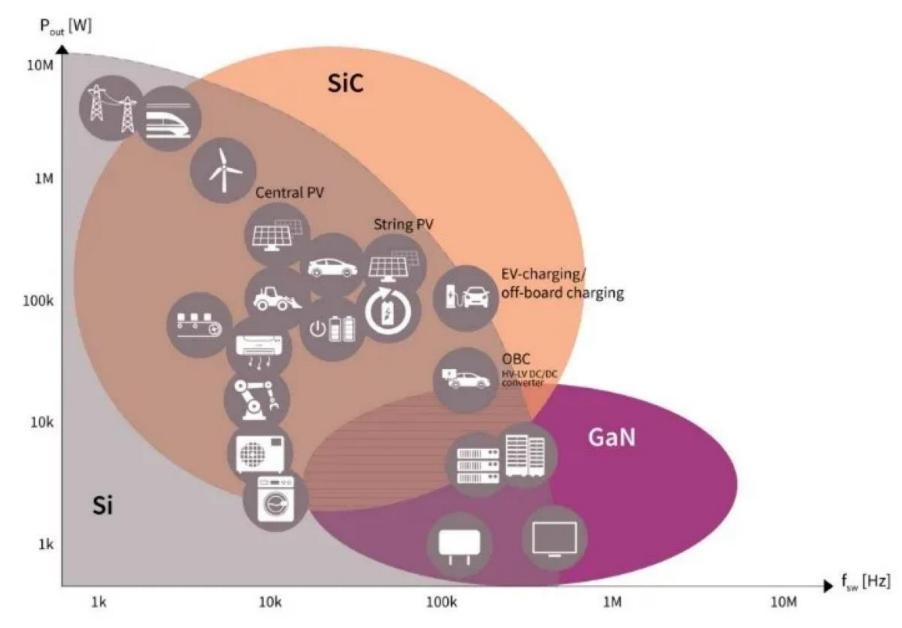

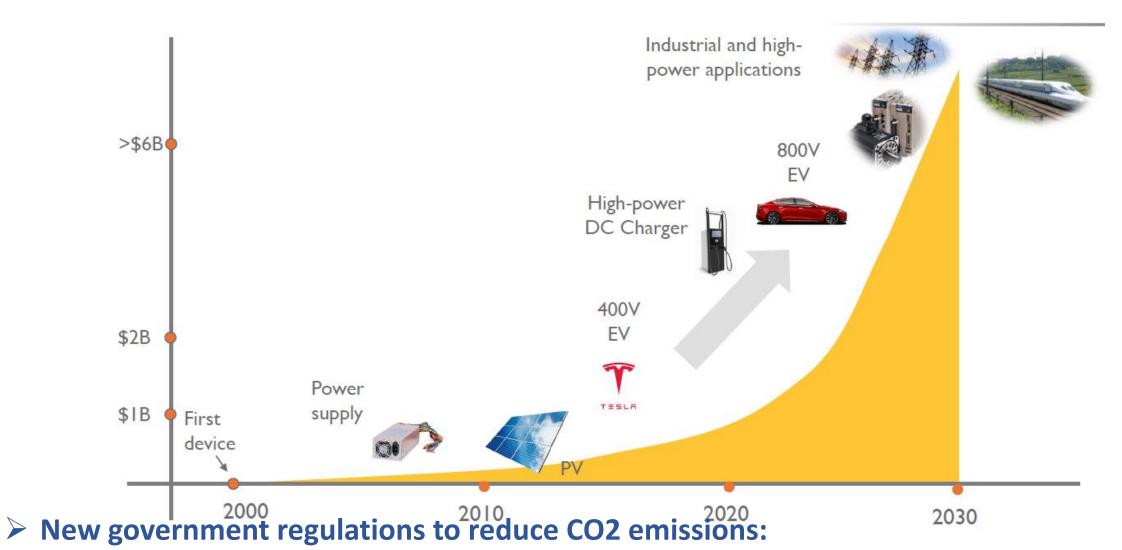

#### **Motivation for SiC**

#### SiC vs. GaN

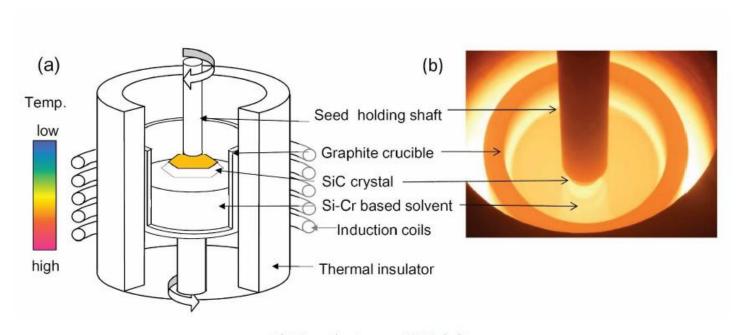

#### **SiC Crystal Growth**

SiC Growth - Source: CS Website

- **➤ SiC Boule Growth Process:**

- Very slow (> 2 weeks)

- > Crystal defects are still a problem

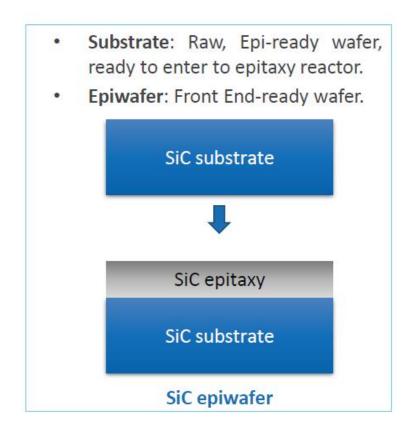

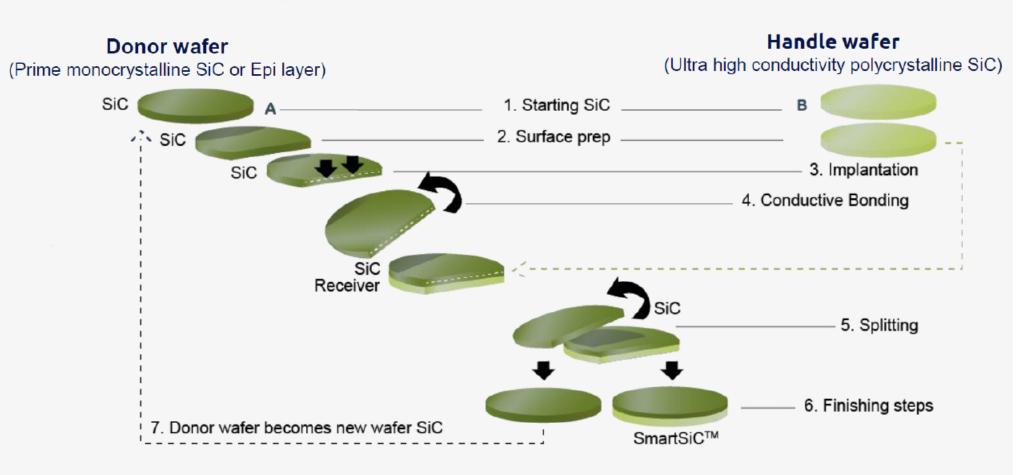

# **SOITEC Revolutionary Breakthrough**

SmartSiC™, an adaptation of Smart Cut™ process to SiC

- > Adaptation of SmartCut to SiC wafer production:

- > The single crystal SiC donor wafer can be reused up to 20 times

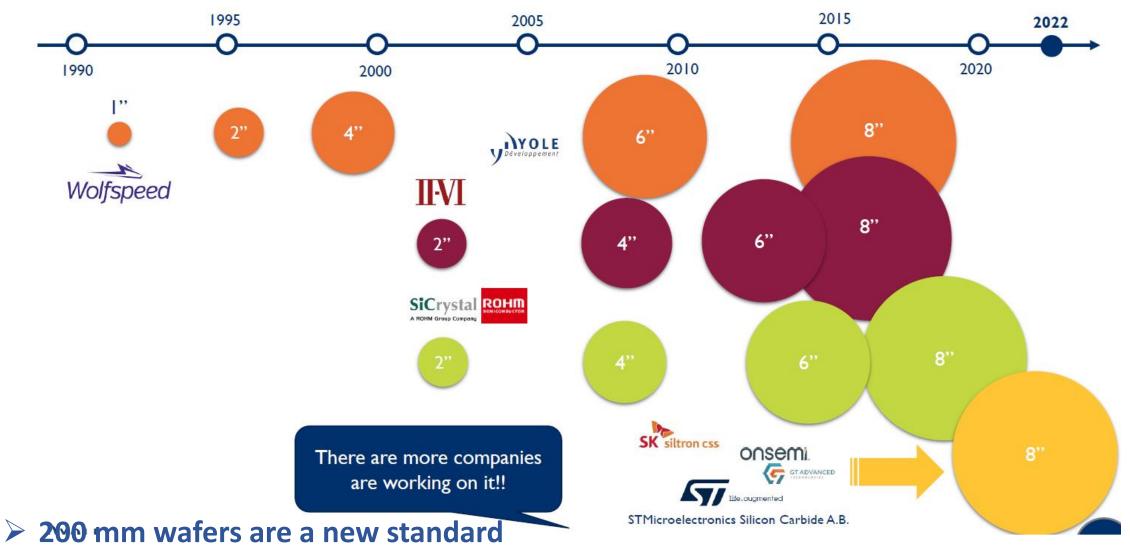

#### **SiC Wafer Size Evolution**

- Vertical integration is a new trend

- From SiC boule growth to the SiC Module Production (e.g., ST)

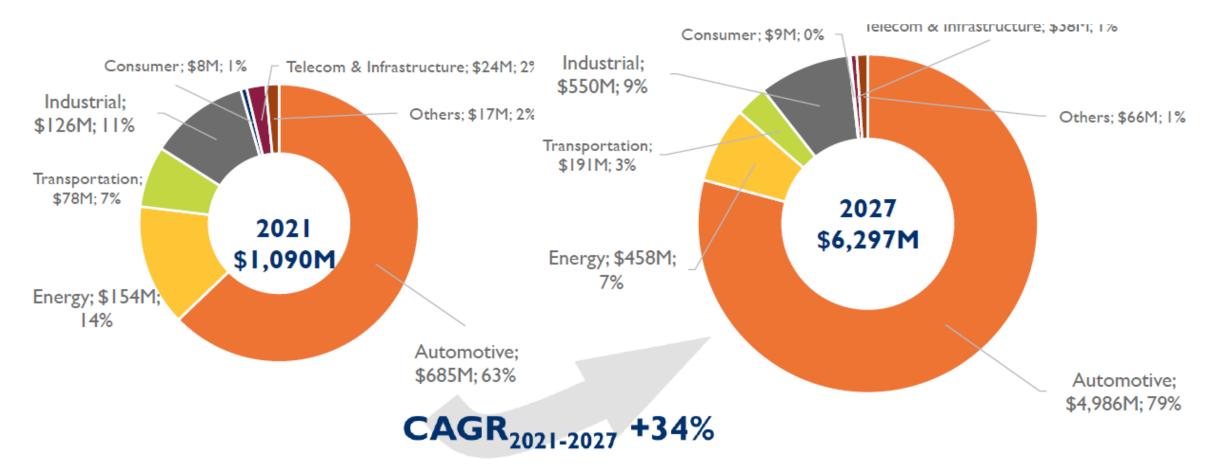

#### **SiC Market Growth Prediction**

- > Fastest growth rate in semiconductor industry:

- Demand driven by Battery Electric Vehicles

#### **SiC Market Size Explosion**

➢ By 2035 the demand for 200mm SiC wafers will exceed the current worldwide production of all TSMC fabs